Southwest Microwave, Inc.

'via Blog this'

Friday, December 19, 2014

Wednesday, December 3, 2014

Monday, December 1, 2014

Wednesday, November 19, 2014

Soldermask - TAIYO PSR-4000BN Series

Wednesday, November 12, 2014

Thursday, November 6, 2014

Creation Technologies | Our Locations

Creation Technologies | Locations:

Creations Technologies is Circuit Board Contract Manufacturer with a global footprint.

Bookmark Only ! (Not an endorsement)

I have not conducted business with Creations Technologies.

Creations Technologies is Circuit Board Contract Manufacturer with a global footprint.

Bookmark Only ! (Not an endorsement)

I have not conducted business with Creations Technologies.

Friday, October 17, 2014

Wednesday, October 8, 2014

The Perfect Stackup for High Speed Design

Click on Image to View

http://www.icd.com.au/articles/Perfect_Stackup_PCB-Nov2011.pdf

'via Blog this'

http://www.icd.com.au/articles/Perfect_Stackup_PCB-Nov2011.pdf

'via Blog this'

Friday, September 12, 2014

Microtek Laboratories | Testing and Training Resources

Microtek Laboratories | Testing and Training Resources:

'via Blog this'

Regarding PCB and PCA reliability.

Plated through hole integrity is the most important metric

to monitor.

Vias are small plated through holes used to connect signals

passing from one layer to another layer.

90% of all bare board pcb failures (open and shorts) can be

traced to bad vias. That being said, reviewing cross sectioned samples of your boards prior to assembly is a critical to ensure long term reliability of your products.

'via Blog this'

Thursday, September 11, 2014

Friday, September 5, 2014

PCBDESIGN007 Isola's I-Speed Endorsed as Laminate Choice for PCBs

"I-Speed has been endorsed by two leading companies as the laminate of choice for PCBs using sequential lamination technology, requiring high conductive anodic filament (CAF) reliability and improved, cost effective signal integrity."

Source:

PCBDESIGN007 Isola's I-Speed Endorsed as Laminate Choice for PCBs:

'via Blog this'

Source:

PCBDESIGN007 Isola's I-Speed Endorsed as Laminate Choice for PCBs:

'via Blog this'

CTE-Z - RoHs Thermal Stresses on VIAs

How To PCB - Thermal: Jack Olsen

Jack has an excellent description about CTE-Z and the thermal stresses RoHs reflow has on vias.

Visit Jack Olsen's site 'How to PCB' to see the full article.

Click here to view the thermal stress animation.

The Z axis stresses can cause vias and traces to fracture.

See the link above to visit Jack's site and read the article.

Jack has an excellent description about CTE-Z and the thermal stresses RoHs reflow has on vias.

Visit Jack Olsen's site 'How to PCB' to see the full article.

Click here to view the thermal stress animation.

The Z axis stresses can cause vias and traces to fracture.

See the link above to visit Jack's site and read the article.

Hipot Testing Articles

Best Methods for Safe Hipot Testing - Slaughter

Understanding HiPot Certification Testing - Electronic Design

'via Blog this'

Understanding HiPot Certification Testing - Electronic Design

'via Blog this'

Monday, September 1, 2014

Differential Pair Routing

"This application note discusses the selection and optimal settings of differential pair design rules. When it comes to successfully deploying differential signals in high-speed designs, symmetry is the key."

Barry sums it up nicely.

"In Conclusion

1. Symmetry is the key to successfully deploying differential signals in high-speed designs. Maintaining the equal and opposite amplitude and timing relationship is the principal concept when using differential pairs.

2. Match the length of each signal of the pair. This ensures that there is no skew between the signals of the pair and flight times will be identical.

3. Route the differential pairs to impedance and at the optimal spacing: Gap = 2 x trace width.

4. To control crosstalk, keep aggressors far away from differential pairs, especially on

Microstrip (outer layers). A good rule of thumb here is Gap = 3 x trace width. PCB"

'via Blog this'

Barry sums it up nicely.

"In Conclusion

1. Symmetry is the key to successfully deploying differential signals in high-speed designs. Maintaining the equal and opposite amplitude and timing relationship is the principal concept when using differential pairs.

2. Match the length of each signal of the pair. This ensures that there is no skew between the signals of the pair and flight times will be identical.

3. Route the differential pairs to impedance and at the optimal spacing: Gap = 2 x trace width.

4. To control crosstalk, keep aggressors far away from differential pairs, especially on

Microstrip (outer layers). A good rule of thumb here is Gap = 3 x trace width. PCB"

'via Blog this'

Sunday, August 31, 2014

Transmission Line Terminations

Managing Signal Quality - Hyperlynx

Friday, August 29, 2014

Sunday, August 24, 2014

Common Trace Transmission Problems and Solutions

Saturday, August 23, 2014

Hyperlynx / Altera - Tco

"This application note describes the output timing parameters for Altera® devices, explains how Altera defines tCO results, and presents techniques for calculating the output timing for your system. In addition, a sample DDR2 interface link is presented and analyzed for calculating output timing"

http://www.altera.com/literature/an/an366.pdf

'via Blog this'

http://www.altera.com/literature/an/an366.pdf

'via Blog this'

Friday, August 22, 2014

VIA - Covering Recommendations

There are different and conflicting opinions when it comes to best practices for covering vias (tenting, filling or capping).

This is due to information that lingers in the cloud (internet) once it has been posted.

Here are my recommendations for reliability based on best known current practices.

click on image to view

click on image to view

Tented Vias (Not Recommended)

Why? Trapped etchant chemicals can corrode the vias over time.

"This type of via can be subject to the "micro-etch" process. This is caused by a small amount of residual etchant trapped inside a tented via. This material will crystallize rapidly, creating copper sulfate crystals. Over time, these crystals can cause long term reliability issues. In the case of a electroless nickel immersion gold (ENIG) finish, the gold and small area of exposed copper near the tent could form a galvanic cell, accelerating the etch process"

Source: TI - http://www.ti.com/lit/an/sprabb3/sprabb3.pdf see page 18.

Plugged Vias (Not Recommended)

Why? Trapped etchant chemicals can corrode the vias over time.

Same issue as the one sided tented via.

"Since it is only partially filled, chemical entrapment is a major concern."

Source: TI - http://www.ti.com/lit/an/sprabb3/sprabb3.pdf

Filled Vias (Highly Recommended)

Why ? Higher Reliability.

"Filled vias are 100% filled, usually with a non-conductive material. This process uses additional process steps. This is done to ensure 100% of the vias are covered.

There are several variations of the filled via.

A filled and covered via has a secondary covering of material (liquid or dry film solder mask) applied over the via. It may be applied from either one side or both sides."

Expensive $$.

Via in Pad VIP (Recommended)

"This is the ultimate via and is commonly called Via-In-Pad (VIP). Vias are filled with a conductive or non-conductive media, planarized and then plated over. This process allows the use of via capture pads as SMD pads.

VIP has become very common in BGA PCB designs to reduce routing issues and lower inductance associated with high speed connections. However, it does drive up the overall PCB cost. If at all possible, consider other alternatives and use VIP only as a last resort."

VIP has become very common in BGA PCB designs to reduce routing issues and lower inductance associated with high speed connections. However, it does drive up the overall PCB cost. If at all possible, consider other alternatives and use VIP only as a last resort."

Source: TI - http://www.ti.com/lit/an/sprabb3/sprabb3.pdf

Cons: Most expensive $$$.

Soldermask Relieved (Recommended)

Soldermask relieved vias have the soldermask pulled back from the drilled hole. Typically the mask open is drill + 5mils. Note finished plating in via barrel (ENIG).

Open vias allows for rinsing and cleaning of the vias to remove any trapped enchants.

Soldermask Relieved (Recommended)

Soldermask relieved vias have the soldermask pulled back from the drilled hole. Typically the mask open is drill + 5mils. Note finished plating in via barrel (ENIG).

Open vias allows for rinsing and cleaning of the vias to remove any trapped enchants.

Via Encroachment (Recommended)

Leave the via open and relief the soldermask at via barrels.

Pros: Low Cost, Good Heat Sink

Cons: Solder wicking, paste volume needs to be compensated. Solder bumps can appear on bottom side if paste volume is not properly compensated.

Fab Note:

VIA IN PAD: SOLDER MASK ENCROACHED VIAS (DRILL SIZE 8.1 MILS)

References:

Texas Instruments:

Eurocircuits Printed circuits blog

Advanced Circuits

Thursday, August 21, 2014

Wednesday, August 20, 2014

Samtec Signal Integrity Book

Connector Pin Mapping

"By assigning pins between signals as return paths (grounds), unwanted coupling between signal pins can be minimized. For high speed applications a 1:1 signal to ground ratio is typically optimal. Pin mapping for SE applications would then be S-G-S-G, while DP applications would use DP-G-DP-G.

These pin assignments provide a good performance versus density trade-off. Of course, more return paths could be added between signals to increase isolation for applications where crosstalk must be extremely low. However, this greatly reduces signal density of the interconnect."

Source: Samtec Signal Integrity Book

"By assigning pins between signals as return paths (grounds), unwanted coupling between signal pins can be minimized. For high speed applications a 1:1 signal to ground ratio is typically optimal. Pin mapping for SE applications would then be S-G-S-G, while DP applications would use DP-G-DP-G.

These pin assignments provide a good performance versus density trade-off. Of course, more return paths could be added between signals to increase isolation for applications where crosstalk must be extremely low. However, this greatly reduces signal density of the interconnect."

Source: Samtec Signal Integrity Book

Sharpen rising and falling edges | EDN

"Wherever you find a digital control signal, you find sharp rising and falling edges that need characterization. These edges occur on switching power supplies that drive power MOSFETS and they occur in logic gates. Unless your measurement system—oscilloscope and probe—have sufficient bandwidth and sample rate.

POL (point of load) switching regulators have reached 1nS edge speed and off-the-shelf high-speed logic gates, such as the NC7SZ04, have rise times of roughly 500 pSec. While many engineers measure edges on these components, they are likely getting incorrect results. The right system bandwidth will result in cleaner, more accurate measurements."

Source: Sharpen rising and falling edges | EDN:

Excellent article which demonstrates the bandwidth requirements of an O'scope to properly measure signals with 1nS or faster rising and falling edges.

'via Blog this'

POL (point of load) switching regulators have reached 1nS edge speed and off-the-shelf high-speed logic gates, such as the NC7SZ04, have rise times of roughly 500 pSec. While many engineers measure edges on these components, they are likely getting incorrect results. The right system bandwidth will result in cleaner, more accurate measurements."

Source: Sharpen rising and falling edges | EDN:

Excellent article which demonstrates the bandwidth requirements of an O'scope to properly measure signals with 1nS or faster rising and falling edges.

'via Blog this'

Comparing Microstrip and CPW Performance

TxLine 2003 - Impedance Calculator

One of my favorite Impedance Calculators is TxLine 2003.

This calculator is quite good, the CBCPW calculation is the best I have found.

Here a screen shot of the microstrip calculation.

For microstrip calculations, the Effective Dielectric Constant is derived from a combination of the resin, glass and air. It does not include the effects of soldermask. However it good enough to get you within 50 ohms +/- 5%.

Phase Constant

Phase Constant sounds like something complicated, until you realize it's nothing more than angular rotation of phase in degrees of a sine wave for a selected unit of length.

In the screen shot above I intentionally manipulated the Dielectric Constant (Er) while keeping the electrical length set to 360 degrees until the phase Constant equaled 60 degrees.

As shown the Physical length of the microstrip at 1GHz wtih a dielectric constant of 5.62213 equals 60 degrees per inch. So 6 inches = 360 degrees (6 x 60 = 360). Pretty simple math.

Critical Length

We have often heard about the term critical trace length for high speed and RF designs. Most often you hear numbers like 1/7 or 1/10 of a wavelength as being the critical trace length.

The critical trace length is simply the length at which you must use a good transmission line to send transmit and receive signals and on your PCB.

Digital circuit designers are familiar with Rule of Thumb #1 Bandwidth of a signal from its rise time.

This calculator is quite good, the CBCPW calculation is the best I have found.

Here a screen shot of the microstrip calculation.

For microstrip calculations, the Effective Dielectric Constant is derived from a combination of the resin, glass and air. It does not include the effects of soldermask. However it good enough to get you within 50 ohms +/- 5%.

Phase Constant

Phase Constant sounds like something complicated, until you realize it's nothing more than angular rotation of phase in degrees of a sine wave for a selected unit of length.

In the screen shot above I intentionally manipulated the Dielectric Constant (Er) while keeping the electrical length set to 360 degrees until the phase Constant equaled 60 degrees.

As shown the Physical length of the microstrip at 1GHz wtih a dielectric constant of 5.62213 equals 60 degrees per inch. So 6 inches = 360 degrees (6 x 60 = 360). Pretty simple math.

Critical Length

We have often heard about the term critical trace length for high speed and RF designs. Most often you hear numbers like 1/7 or 1/10 of a wavelength as being the critical trace length.

The critical trace length is simply the length at which you must use a good transmission line to send transmit and receive signals and on your PCB.

Digital circuit designers are familiar with Rule of Thumb #1 Bandwidth of a signal from its rise time.

Tuesday, August 19, 2014

VIA Spacing for RF and Highspeed Designs

A good rule of thumb is 1/8 wavelength of the highest frequency of interest.

"In RF design we typically need to work with only the fundamental frequency of operation. For instance: In a 2.4-GHz RF design the goal is to have a nice 2.4-GHz sine wave on our board with low harmonics. The frequencies that we need to be concerned with are really 2.4 GHz.

In digital design, the goal is to have a nice square wave on our board. A 1GHz digital data signal needs to be square for a good eye diagram. This means that the true operating bandwidth of these traces needs to be at least five times the fundamental frequency or 5GHz. This is from the rule of thumb that for a good-quality digital signal you need to pass at least the 5th harmonic of that signal."

Critical guidelines for RF and microwave PCB Design | Embedded

Critical guidelines for RF and microwave PCB Design | Embedded:

Crosstalk is discussed in this article

'via Blog this'

Crosstalk is discussed in this article

'via Blog this'

PDNDesigner | Giga Hertz Technology

Monday, August 18, 2014

Signal Integrity - Guidelines

Stripline traces passing over a split plane should be at least four times farther from the signal than the reference plane. Source: Eric Bogatin

If a signal changes reference planes when passing through a via, add an adjacent ground via.

Source : Signal Consulting Inc. Dr. Johnson

Use a capacitor to AC couple the return path when reference planes are at different potentials.

Source: TDK Outline of EMC Design Methods

This article compares the propagation delay (tpd) for serpentine, spiral, and straight traces.

The results show that a signal will travel faster in a microstrip serpentine trace compared to a straight trace of the same length. And the stripline serpentine trace will lag the straight trace.

Source: A New Slant on Matched-Length Routing - Barry Olney

Serpentine Gaps should be 3 x height to nearest reference plane.

When a design requires equal-length traces between the source and multiple loads, you can bend some traces to match trace lengths (see Figure 11–20). However, improper trace bending affects signal integrity and propagation delay.

To minimize crosstalk, ensure that S ≥ 3 × H, where S is the spacing between the parallel sections and H is the height of the signal trace above the reference ground plane.

Click on images to view

Differential Pairs

D = distance between two differential pair signals; W = width of a trace in a differential pair; S = distance between the traces in a differential pair; and H = dielectric height above the group plane.

If a signal changes reference planes when passing through a via, add an adjacent ground via.

Source : Signal Consulting Inc. Dr. Johnson

Use a capacitor to AC couple the return path when reference planes are at different potentials.

Source: TDK Outline of EMC Design Methods

This article compares the propagation delay (tpd) for serpentine, spiral, and straight traces.

The results show that a signal will travel faster in a microstrip serpentine trace compared to a straight trace of the same length. And the stripline serpentine trace will lag the straight trace.

Source: A New Slant on Matched-Length Routing - Barry Olney

Serpentine Gaps should be 3 x height to nearest reference plane.

When a design requires equal-length traces between the source and multiple loads, you can bend some traces to match trace lengths (see Figure 11–20). However, improper trace bending affects signal integrity and propagation delay.

To minimize crosstalk, ensure that S ≥ 3 × H, where S is the spacing between the parallel sections and H is the height of the signal trace above the reference ground plane.

Click on images to view

Differential Pairs

D = distance between two differential pair signals; W = width of a trace in a differential pair; S = distance between the traces in a differential pair; and H = dielectric height above the group plane.

- Ensure that D > 2S to minimize the crosstalk between the two differential pairs.

- Place the differential traces S = 3H as they leave the device to minimize reflection noise.

- Keep the length of the two differential traces the same to minimize the skew and phase difference.

- Avoid using multiple vias because they can cause impedance mismatch and inductance.

PCB design course & checklist | EDN

IBIS Models

Texas Instruments

The IBIS model, Part 1: A conduit into signal-integrity analysis

The IBIS model, Part 2: Determining the quality of a model

The IBIS model, Part 3: Investigating Signal Integrity Issues

Analog Devices

IBIS Models: How they are Generated

The IBIS model, Part 1: A conduit into signal-integrity analysis

The IBIS model, Part 2: Determining the quality of a model

The IBIS model, Part 3: Investigating Signal Integrity Issues

Analog Devices

IBIS Models: How they are Generated

MultiSIM BLUE

MultiSIM BLUE:

"MultiSIM BLUE Coming Soon! NI Component Evaluator – Mouser Edition MultiSIM BLUE allows you to scheme, simulate, PCB layout, BOM and purchase – all in one powerful tool. Even better, the entire tool chain is fully integrated. No more going back and forth between different programs. MultiSIM BLUE provides engineers an easy-to-use, seamless environment for the functional simulation of linear circuits using the Berkeley SPICE engine and advanced electronic components from the industry’s leading manufacturers."

'via Blog this'

"MultiSIM BLUE Coming Soon! NI Component Evaluator – Mouser Edition MultiSIM BLUE allows you to scheme, simulate, PCB layout, BOM and purchase – all in one powerful tool. Even better, the entire tool chain is fully integrated. No more going back and forth between different programs. MultiSIM BLUE provides engineers an easy-to-use, seamless environment for the functional simulation of linear circuits using the Berkeley SPICE engine and advanced electronic components from the industry’s leading manufacturers."

'via Blog this'

Molex Pin Map Configurator

Molex Pin Map Configurator:

Signal Integrity Support from Molex for Backplane Connectors, nice !

Video Link

'via Blog this'

Signal Integrity Support from Molex for Backplane Connectors, nice !

Video Link

'via Blog this'

Friday, August 15, 2014

Tuesday, August 5, 2014

Why White Residue Forms on PCBs

“It’s easy to determine the type

of contamination you have on the board. Test

each patch of residue with drops

of water or alcohol (IPA). If the drops of water

dissolve the residue, its ionic;

if dissolved by the alcohol, the residue is organic.

This quickly tells you what it

will take to clean the board (either a water-based

cleaner or a solvent-based

cleaner), and can give you some indication of what

is causing the problem. In both

cases, it’s more likely to be improper techniques or incomplete

cleaning that causes the contamination problem.”

Source: http://tayloredge.com/reference/Science/solder_cleaning.pdf

'via Blog this'

Monday, August 4, 2014

Friday, August 1, 2014

Effective PCB Designs - Connector Signal Integrity

Serpentine Routing - Gaps

When a design requires equal-length traces between the source and multiple loads, you can bend some traces to match trace lengths (see Figure 11–20). However, improper trace bending affects signal integrity and propagation delay. To minimize crosstalk, ensure that S ≥ 3 × H, where S is the spacing between the parallel sections and H is the height of the signal trace above the reference ground plane (see Figure 11–21).

Click on images to view

Source Altera: High-Speed Board Layout Guidelines.

Also see: A New Slant on Matched-Length Routing - Barry Olney

This article compares the delay (tpd) for serpentine, spiral, and straight traces.

The results show that a signal will travel faster in a microstrip serpentine trace compared to a straight trace of the same length. And the stripline serpentine trace will lag the straight trace.

Click on images to view

Source Altera: High-Speed Board Layout Guidelines.

Also see: A New Slant on Matched-Length Routing - Barry Olney

This article compares the delay (tpd) for serpentine, spiral, and straight traces.

The results show that a signal will travel faster in a microstrip serpentine trace compared to a straight trace of the same length. And the stripline serpentine trace will lag the straight trace.

How Via Stubs Distort High Speed Signals

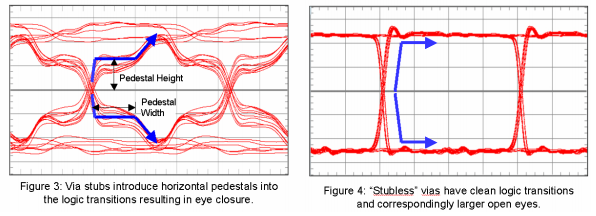

Figures 3 and 4 show representative eye-diagrams of two via structures, one with an intact stub and one without a stub.

Comparing Figures 3 and 4, one can see that via stubs introduce horizontal pedestals in the logic 0-to-1 and logic 1-to-0 transitions. These pedestals close the eye, making it more difficult for the digital receiver to ascertain whether the received signal is truly a logical one or a logical zero.

Source: Overview of Backdrilling - Sanmina:

Click image to view

See the link above for the full article.

More about stubs from Altera: High-Speed Board Layout Guidelines.

Daisy Chain Routing With Stubs

Daisy chain routing is a common practice in designing PCBs. One disadvantage of daisy chain routing is that stubs, or short traces, are usually necessary to connect devices to the main bus (see Figure 11–14). If a stub is too long, it will induce transmission line reflections and degrade signal quality.

Therefore, the stub length should not exceed the following conditions:

TDstub < (T10% to 90%) / 3

where TDstub = Electrical delay of the stub

T10% to 90% = Rise or fall time of signal edge

For a 1-ns rise-time edge, the stub length should be less than 0.5 inches

(see the “References” section). If your design uses multiple devices, all

stub lengths should be equal to minimize clock skew.

'via Blog this'

Comparing Figures 3 and 4, one can see that via stubs introduce horizontal pedestals in the logic 0-to-1 and logic 1-to-0 transitions. These pedestals close the eye, making it more difficult for the digital receiver to ascertain whether the received signal is truly a logical one or a logical zero.

Source: Overview of Backdrilling - Sanmina:

Click image to view

See the link above for the full article.

More about stubs from Altera: High-Speed Board Layout Guidelines.

Daisy Chain Routing With Stubs

Daisy chain routing is a common practice in designing PCBs. One disadvantage of daisy chain routing is that stubs, or short traces, are usually necessary to connect devices to the main bus (see Figure 11–14). If a stub is too long, it will induce transmission line reflections and degrade signal quality.

Therefore, the stub length should not exceed the following conditions:

TDstub < (T10% to 90%) / 3

where TDstub = Electrical delay of the stub

T10% to 90% = Rise or fall time of signal edge

For a 1-ns rise-time edge, the stub length should be less than 0.5 inches

(see the “References” section). If your design uses multiple devices, all

stub lengths should be equal to minimize clock skew.

'via Blog this'

Subscribe to:

Posts (Atom)