METRIC PITCH BGA AND MICRO BGA ROUTING SOLUTIONS - Tom Hausherr

This white paper includes a Common Via Padstacks Table

'via Blog this'

Sunday, June 30, 2013

Friday, June 28, 2013

WEBENCH Export – TI.com

WEBENCH Export – TI.com:

The WEBENCH Export option will take any Power Designer design and convert it on the fly to leading CAD development platforms. Designers using the industry-leading tools from Altium, Cadence, or Mentor Graphics can immediately go from easy-to-use, expert system, value-optimized designs created online in the no-cost WEBENCH Designer or Architect platforms directly into their CAD software. WEBENCH Export users can open a design in their software just as if they spent days or weeks creating it natively.

WEBENCH Export allows the direct download of dynamic WEBENCH designs into leading CAD environments in minutes.

DFM - Thermal Reliefs Pros and Cons

Thermal reliefs added to RF connector ground pins will allow for easier hand soldering.

Here's some of the advantages of NO thermal reliefs:

http://electronics.stackexchange.com/questions/14435/why-thermal-reliefs-on-vias

Here's some of the advantages of NO thermal reliefs:

http://electronics.stackexchange.com/questions/14435/why-thermal-reliefs-on-vias

Tuesday, June 25, 2013

Monday, June 24, 2013

Decoupling Caps

Decoupling Caps - Harry Ott:

“There

are a large number of people that use and/or recommend the use of multiple

capacitors of different values. My recommendation is don't! The

problem with this approach is that the different value capacitors produce an

anti-resonance, or cross-resonance (which produces an impedance peak).

Not a desirable result! For those still considering the use of different

value capacitors I would suggest that you look at the Bruce Archambeault and Clayton

Paul papers referenced below. The Bruce Archambeault paper in particular gives measured values of

decoupling effectiveness, using a network analyzer.”

Saturday, June 22, 2013

Tuesday, June 18, 2013

VIAs - Annular Rings

IPC6012 Acceptance Criteria for Annular Rings

The following screen shot is from an eptac webinar presentation titled:

Interpreting IPC-A-600 Requirements for Annular Rings and Laminate Cracks

Source: webinar_eptac_07_21_10.pdf

PCB fab notes for commercial board designs typically call out IPC6102 Class 2 requirements.

However it is not uncommon to see exceptions in fab notes which call for the annular rings of the vias to meet a minimum finished width of 2mils.

To meet these minimum annular ring requirements the fabricators may need to increase the pad diameter.

Example 20/10:

If you have used 20/10mil VIAs and stated in the fab notes that minimum 2mil annular rings are required, the fabricator will need to increase the pad size to 23mils to meet this requirement.

The variables include finished hole size requirements shown in the drill table. The actual drill size used to drill holes is +4mils to 5mils larger than the finished hole size to allow for plating in the barrel. Plus true position tolerances (+/- 3mil) for the drilled holes, plus layer to layer registration tolerances (+/-3mils).

Do NOT make Assumptions:

You should not assume that the 13mil difference in the above example will apply to any size via. As the hole size increases the fabricator will require proportionally larger pads.

Let say you have assumed the 13mil difference above would be good enough for a 43/30mil via or plated hole. To meet the 2mil annular ring requirement your fabricator will ask for a pad size that is ~16mils larger than the finished hole size. So in this example you would need a 46mil pad, to meet the 2 mil annular ring requirement.

To avoid surprises, talk to your PCB Fabricator.

The following screen shot is from an eptac webinar presentation titled:

Interpreting IPC-A-600 Requirements for Annular Rings and Laminate Cracks

Source: webinar_eptac_07_21_10.pdf

PCB fab notes for commercial board designs typically call out IPC6102 Class 2 requirements.

However it is not uncommon to see exceptions in fab notes which call for the annular rings of the vias to meet a minimum finished width of 2mils.

To meet these minimum annular ring requirements the fabricators may need to increase the pad diameter.

Example 20/10:

If you have used 20/10mil VIAs and stated in the fab notes that minimum 2mil annular rings are required, the fabricator will need to increase the pad size to 23mils to meet this requirement.

The variables include finished hole size requirements shown in the drill table. The actual drill size used to drill holes is +4mils to 5mils larger than the finished hole size to allow for plating in the barrel. Plus true position tolerances (+/- 3mil) for the drilled holes, plus layer to layer registration tolerances (+/-3mils).

Do NOT make Assumptions:

You should not assume that the 13mil difference in the above example will apply to any size via. As the hole size increases the fabricator will require proportionally larger pads.

Let say you have assumed the 13mil difference above would be good enough for a 43/30mil via or plated hole. To meet the 2mil annular ring requirement your fabricator will ask for a pad size that is ~16mils larger than the finished hole size. So in this example you would need a 46mil pad, to meet the 2 mil annular ring requirement.

To avoid surprises, talk to your PCB Fabricator.

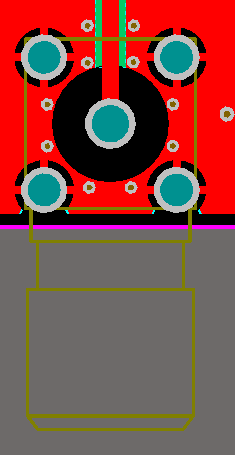

VIA Barrel Reliefs - Soldermask

Using Soldermask Barrel Reliefs can provide a reliable low cost alternative to using fills and plugs.

Vias with Finished Holes Sizes greater than 18mils that are NOT FILLED should be un-tented using Soldermask Barrel Reliefs.

When the nominal finished hole sizes of vias are larger than 18mils fabricators may request to add barrel reliefs to the soldermask.

Some Fabricators will tent vias with holes sizes as large as 23mils (0.6mm) using LPI soldermask. Larger holes may require additional processing steps.

Consult with your fabricator when using soldermask barrel reliefs. The hole size threshold and soldermask relief requirements for using barrel reliefs will vary from fabricator to fabricator.

The soldermask reliefs are typically specified as finished hole size + 6mils.

For vias with hole sizes smaller than 18mils (0.45mm) fabricators can fully tent the vias on both sides of the board using LPI soldermask application techniques.

For vias with hole sizes larger than 18mils soldermask barrel reliefs can be used to minimize problems associated with trapped etching and plating solutions.

The open vias allow for rinsing and cleaning of the via barrels after the finished plating process, this reduces trapped corrosive chemicals in the via barrels.

Top Layer View

Bottom Layer View

.

When using barrel reliefs for vias the minimum soldermask web rules need to be considered.

A barrel relief via needs to be placed farther away from the component pad than a completely tented via.

As shown above the via at R220 will violate the 4mil (0.1mm) minimum soldermask web rule.

See C221 for a good example which has greater than 4mils of soldermask web.

If you plan to use an In Circuit Tester (ICT) with a vacuum system you may not want to use barrel reliefs.

A large number of holes in the board may limit the vacuum system's ability to properly mate the the board with the test probes.

When using barrel reliefs on vias, as shown below it can be difficult to avoid having some silkscreen printed on barrel relieved vias.

You may need to adjust your design rules and fab notes to accommodate the silkscreen, or position the silkscreen to avoid printing ink in the via holes.

Tenting vias only on one side can cause problems. Trapped etching chemicals in vias will corrode the barrel walls and create open circuits over time.

Vias with Finished Holes Sizes greater than 18mils that are NOT FILLED should be un-tented using Soldermask Barrel Reliefs.

When the nominal finished hole sizes of vias are larger than 18mils fabricators may request to add barrel reliefs to the soldermask.

Some Fabricators will tent vias with holes sizes as large as 23mils (0.6mm) using LPI soldermask. Larger holes may require additional processing steps.

Consult with your fabricator when using soldermask barrel reliefs. The hole size threshold and soldermask relief requirements for using barrel reliefs will vary from fabricator to fabricator.

The soldermask reliefs are typically specified as finished hole size + 6mils.

For vias with hole sizes smaller than 18mils (0.45mm) fabricators can fully tent the vias on both sides of the board using LPI soldermask application techniques.

For vias with hole sizes larger than 18mils soldermask barrel reliefs can be used to minimize problems associated with trapped etching and plating solutions.

The open vias allow for rinsing and cleaning of the via barrels after the finished plating process, this reduces trapped corrosive chemicals in the via barrels.

Top Layer View

Bottom Layer View

.

Other things to Consider

When using barrel reliefs for vias the minimum soldermask web rules need to be considered.

A barrel relief via needs to be placed farther away from the component pad than a completely tented via.

As shown above the via at R220 will violate the 4mil (0.1mm) minimum soldermask web rule.

See C221 for a good example which has greater than 4mils of soldermask web.

Test Points

Un-tented vias can be used as test points. The exposed vias can also be useful for prototypes where cuts and jumpers may need to be applied.

ICT Testing with Vacuum Systems

If you plan to use an In Circuit Tester (ICT) with a vacuum system you may not want to use barrel reliefs.

A large number of holes in the board may limit the vacuum system's ability to properly mate the the board with the test probes.

Silkscreen on exposed vias.

When using barrel reliefs on vias, as shown below it can be difficult to avoid having some silkscreen printed on barrel relieved vias.

You may need to adjust your design rules and fab notes to accommodate the silkscreen, or position the silkscreen to avoid printing ink in the via holes.

Avoid using unfilled one-side tented VIAs ! ! !

Workarounds

You may be able to avoid using barrel reliefs by simply using smaller vias that do not require additional process steps.

To handle higher current requirements consider using 2-3 small vias instead of using one large via.

Soldermask - VIA Encroaching

VIA Encroaching can be used to enhance thermal conductivity of the QFN packages.

http://www.cirrus.com/jp/pubs/appNote/AN315REV1.pdf

Tuesday, June 11, 2013

Monday, June 10, 2013

Wednesday, June 5, 2013

Subscribe to:

Comments (Atom)