Using Soldermask Barrel Reliefs can provide a reliable low cost alternative to using fills and plugs.

Vias with Finished Holes Sizes greater than 18mils that are NOT FILLED should be un-tented using Soldermask Barrel Reliefs.

When the nominal finished hole sizes of vias are larger than 18mils fabricators may request to add barrel reliefs to the soldermask.

Some Fabricators will tent vias with holes sizes as large as 23mils (0.6mm) using LPI soldermask. Larger holes may require additional processing steps.

Consult with your fabricator when using soldermask barrel reliefs. The hole size threshold and soldermask relief requirements for using barrel reliefs will vary from fabricator to fabricator.

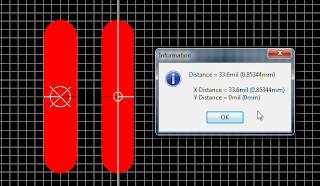

The soldermask reliefs are typically specified as finished hole size + 6mils.

For vias with hole sizes smaller than 18mils (0.45mm) fabricators can fully tent the vias on both sides of the board using LPI soldermask application techniques.

For vias with hole sizes larger than 18mils soldermask barrel reliefs can be used to minimize problems associated with trapped etching and plating solutions.

The open vias allow for rinsing and cleaning of the via barrels after the finished plating process, this reduces trapped corrosive chemicals in the via barrels.

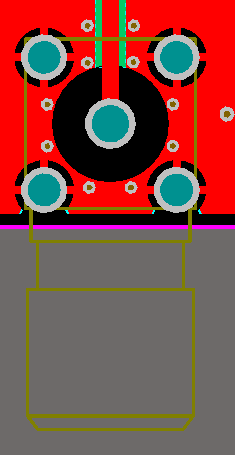

Top Layer View

Bottom Layer View

.

Other things to Consider

When using barrel reliefs for vias the minimum soldermask web rules need to be considered.

A barrel relief via needs to be placed farther away from the component pad than a completely tented via.

As shown above the via at R220 will violate the 4mil (0.1mm) minimum soldermask web rule.

See C221 for a good example which has greater than 4mils of soldermask web.

Test Points

Un-tented vias can be used as test points. The exposed vias can also be useful for prototypes where cuts and jumpers may need to be applied.

ICT Testing with Vacuum Systems

If you plan to use an In Circuit Tester (ICT) with a vacuum system you may not want to use barrel reliefs.

A large number of holes in the board may limit the vacuum system's ability to properly mate the the board with the test probes.

Silkscreen on exposed vias.

When using barrel reliefs on vias, as shown below it can be difficult to avoid having some silkscreen printed on barrel relieved vias.

You may need to adjust your design rules and fab notes to accommodate the silkscreen, or position the silkscreen to avoid printing ink in the via holes.

Avoid using unfilled one-side tented VIAs ! ! !

Tenting vias only on one side can cause problems. Trapped etching chemicals in vias will corrode the barrel walls and create open circuits over time.

Workarounds

You may be able to avoid using barrel reliefs by simply using smaller vias that do not require additional process steps.

To handle higher current requirements consider using 2-3 small vias instead of using one large via.